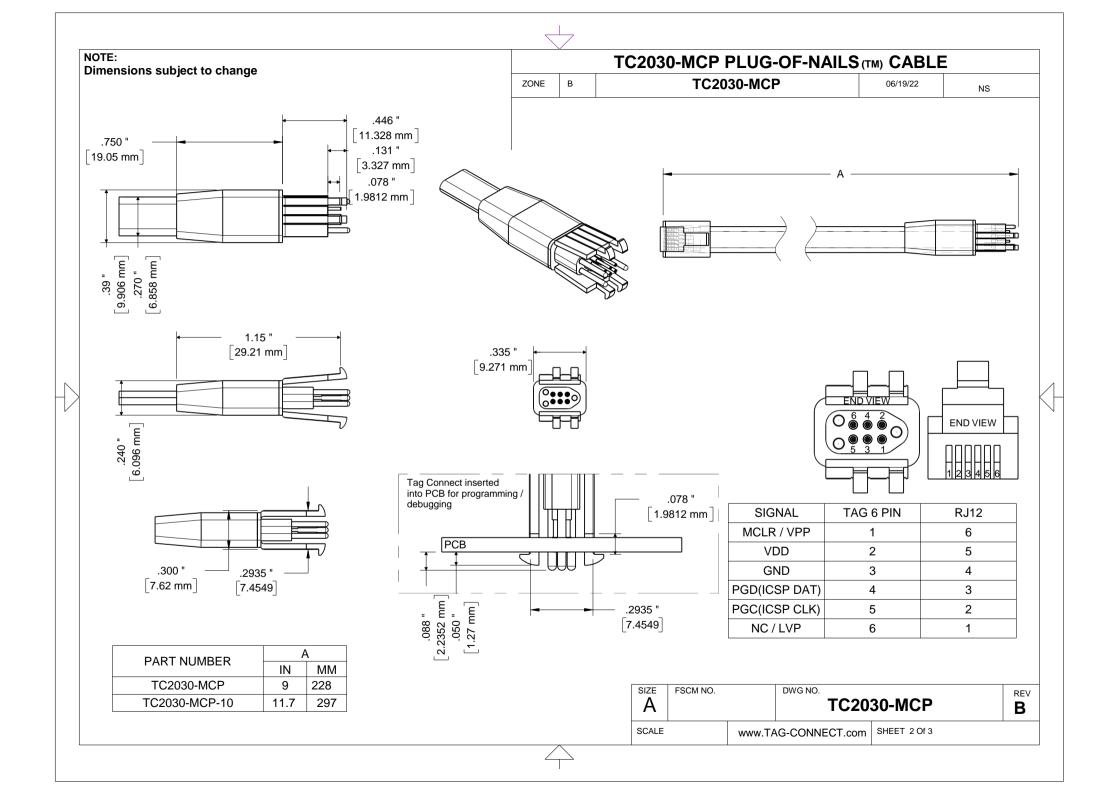

## **Notes:**

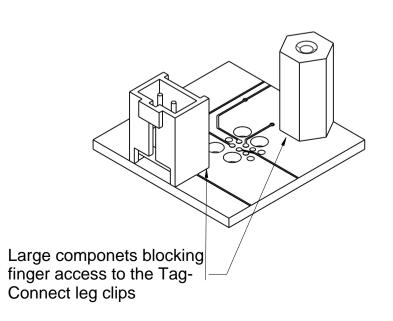

- 1. Allow clearance for finger squeeze access from the two sides shown.

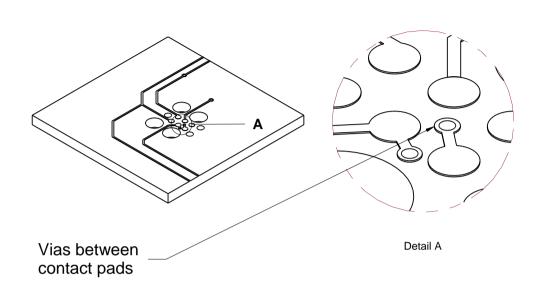

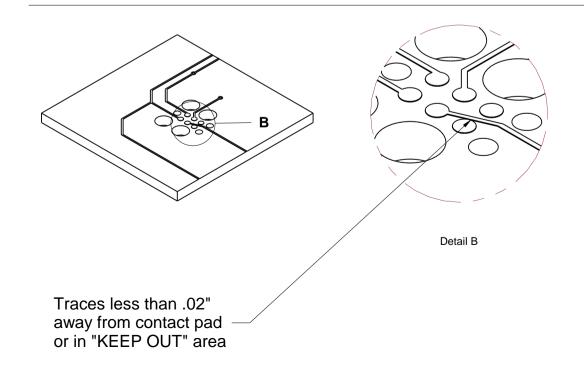

- 2. No tracks or vias in the shaded "KEEP OUT" AREA.

- 3. No other track or signal within .02" of any contact pad.

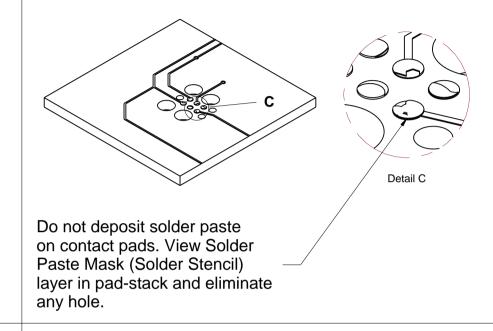

- 4. Do not allow solder paste on the contact pads It is essential to eliminate any hole in the solder paste-mask (solder stencil) layer. If this is not possible make the contact pads thru-hole with a finished hole size of .008" or less.

- 5. Leg and alignment holes may be plated and used as vias but ensure minimum finshed hole size meets specified tolerances.

- 6. To prevent purchasing confusion, please specify DNL in your BOM.

## Allow finger access from this side

FOOTPRINT FOR TC2030-MCP PLUG-OF-NAILS (TM) CABLE

TC2030-MCP-FP

ZONE

1.270 mm

.050

1.270 mm

.040

PCB BOTTOM VIEW

.061 "

1.549 mm

REV

Ø.0935 "± .0030 Ø2.375 mm± .076 NON-PLATED THRU HOLE LEG LATCH HOLES

06/19/22

Ø.039 "± .003 Ø.991 mm± .076 NON-PLATED THRU HOLE ALIGNMENT PIN HOLES

Ø.031 "±.003 Ø.787 mm±.076 CONDUCTIVE CONTACT PADS NO SOLDER PASTE

2 6 5 "KEEP OUT" AREA

Allow finger access from this side

ALLOW A .061 X .046 SQUARE AREA OF CLEARANCE FOR EACH FOOT

.046 "

1.168 mm

SIZE FSCM NO.

FOOTPRINT FOR TC2030-MCP-FP

SHEET 1 Of 3

REV **B**

SCALE WWW.TAG-CONNECT.com

Microchip ICD / ICSP signals

Pin 1: MCLR / Vpp

Pin 2: Vdd

Pin 3: GND Pin 4: PGD (ICSPDAT)

Pin 5: PGC (ICSPCLK)

Pin 6: Unused / LVP

## Layout Problems to Avoid